Esquema del diseño

sábado, 5 de marzo de 2016

Laboratorio No 2

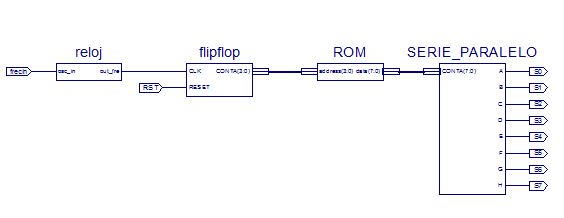

En la aplicación Boole se desarrolla el diseño para un decodificador alfanumérico para luego visualizar en un display de 16 segmentos. Se inicia con el diseño de las letras y números, siguiente con la combinación de entradas y salidas de acuerdo al diseño, para el caso serán 6 entradas y 16 salidas, con la aplicación Boole se genera el código en VHDL

para luego exportar el archivo generado por la aplicación al programa XilinK para hacer el esquemático con los flip flops para la secuencia de conteo, el decodificador alfanumérico y el display de 16 segmentos para la visualización.

viernes, 4 de marzo de 2016

Laboratorio 3

Descripción

de la implementación.

Circuito esquematico.

Entrega del laboratorio

Laboratorio 1

Grupo N: 8CN

María Rosa Villazon Cerquera

Jeisson David Barreto malaver

Edison Alexander Suarez Rodríguez

Se implementó un contador

hexadecimal el cual realizo conteo de 0 hasta 15. El programa se realizó con código

en VHDL teniendo en cuenta la respectiva tabla de verdad, para este caso se requirió

de cuatro entradas y siete salidas y un visualizador display de siete segmentos;

El desarrollo del código se realizó

de la siguiente manera: nuevo

proyecto en esquemático y le adicionamos como Source que se ha elaborado en

Boole, luego de esto le colocamos (;) a las ecuaciones para que permita sintetizar, adicionamos

también el código .ucf que es de la FPGA, para luego activar y renombrar los puertos

que deseamos utilizar, y por ultimo le damos clic Check Syntax y después

Create Schematic Symbol para generar el esquemático, vamos a la pantalla

de esquemático y lo buscamos del archivo del nombre del proyecto, y luego lo

ponemos terminales y las renombramos según la necesidad. Sintetizamos todo,

implementamos diseño y se genera el archivo .bit, y está listo para programar la FPGA .

Suscribirse a:

Comentarios (Atom)