La implementacion de prototipo

sábado, 28 de mayo de 2016

sábado, 16 de abril de 2016

LABORATORIO 7

ALU

CODIGO:

DESCRIPCIÓN DE LA IMPLEMENTACION:

CODIGO:

FOTO DE LA IMPLEMENTACION AVAL PROFESOR

DESCRIPCIÓN DE LA IMPLEMENTACION:

Para este laboratorio lo que implementamos fue realizar una ALU el código

y la finalidad era escoger entre dos

operaciones lógicas y entre dos operaciones

aritméticas las cuales se ven en el código que estamos presentado, una vez

obteniendo los datos, se implementa un contador o una máquinas de estados es nuestro caso lo que implementamos

fue un contador y la razón es que necesitamos que las operaciones se realicen de forma automática y

simplemente haya un reset con el fin

que el usuario cuando desee parar lo

pueda realizar. Para un segundo

plano las operaciones que escogimos fue

en las operaciones aritméticas: la suma, la resta y en las operaciones lógicas lo

que utilizamos fue NOR y la XOR, y para un resultado final el analisis fue conocer un poco a fondo cual fue su funcionamiento aunque lo que realizamos es una pequña parte de las muchas aplicaciones que tiene la alu, podemos observar que para cualquier caso es muy util tener esta herramienta el cual día tras día usa la tecnología.

LABORATORIO 6 MAQUINAS DE ESTADOS

CÓDIGO

FOTO AVAL DEL PROFESOR

DESCRIPCIÓN

Para realizar este laboratorio

fue necesario, tener en claro cómo funcionan las máquinas de estado e

inicialmente realizar el análisis correspondientes

de cada estado en el que se encuentre

para cada estado por lo tanto tendrá un

comportamiento diferencia del estado

actual. En primer paso es conveniente conocer cuáles son las varíables que van a interferir en los estados

y así se debe formar o seleccionar los estados actuales, una vez este

desarrollado las variables las cuales

vamos a intervenir se puede

argumentar y satisfacer la necesidad del

cliente. En segundo lugar es

necesario realizar gráficamente cuales

son los pasos siguientes de forma que al

saltar de un paso al otro sea lo que estamos buscando, en tal caso para tener la

tabla de transición son los estados

siguientes los cuales nos interesa

ubicar con el fin que realice el paso a paso. Y en cuarto lugar lo que buscamos es realizar ya nuestras ecuaciones

finales que obtenemos de la tabla de transición es el resultado final de lo que esperamos obtener.

Lab 8

Descripcion de la implementacion.

En esta implementación de este código se utilizo un monitor con entrada VGA, para poder visualizar en la pantalla nuestra programación de la FPGA, teníamos que adaptar el código de acuerdo a nuestras necesidades, teniendo en cuenta que este solo contaba con 10 ROM, y le adicionamos 12 para que en total nos muestre 22 caracteres según la necesidad del grupo, también toco modificar los ¨slides¨ para que nos diera la capacidad de incluir mas bits en el conteo, ya que con el original era solo de 0 hasta 15 y con la modificación del bit adicional (5 bits) ya nos daba la oportunidad de 0 hasta 31, de los cuales usamos 22 para visualizar el primer nombre de cada integrante del grupo , cada una de las memorias se modifico para que mostrara los datos anteriormente nombrados, y se le dio un nombre diferente para luego mas adelante en el código hacer el llamado a cada una de acuerdo al orden correspondiente, también se modificaron la combinación de colores para generar una imagen diferente de color verde.

Fotografia con aval del docente.

Lab. 5

Descripción de la implementación

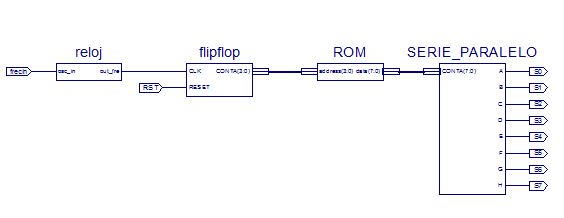

Para

realizar este publik con desplazamiento se utilizó dos reloj, dos contadores

una memoria ROM, 8 registros de desplazamiento paralelo a paralelo, un des

multiplexor de 64 a 8, un alfanum, y dos decos para hacer la conversión a

paralelo, también se utilizó una matriz de 8x8 para visualizar la info.

Luego se procede a diseñar cada letra para poder visualizar en la matriz de 8x8

teniendo en cuenta mayúsculas y minúsculas, y se hace la respectiva combinación

binaria para luego ingresarla a la memoria ROM, se diseñó un reloj 1 a 8 MHz

para el desplazamiento de las letras en la matriz y que sea legible, el

contador llamado 7 el que nos da la cantidad de llamados en la memoria para la

visualización de los nombres de los integrantes del grupo. los registros nos

guardan el dato para cada columna de la matriz, cuando llega el nuevo dato se

lo pasa al siguiente registro para el mismo dato sea visualizado en la

siguiente columna, y así con los demás registros. Además cada registro tiene

una salida de 8 bits y son transferidos al des multiplexor de 64a8 y este

a su vez convierte todo a tan solo 8 bits serial y aquí el Deco2 es quien

realiza la conversión a paralelo que son la entrada para cada una de las

filas de la matriz. Por otro lado tenemos un reloj 2 llamado reloj, este se

diseñó con una frecuencia de 480Mhz y el contador con modulo7, que es el que

realiza la combinación para cada columna, y el Deco para acoplar este

componente con el alfanum que se diseñó con Boole y lógica

inversa ya que las columnas para que se activen deben tener un 0, y ya configurando

puertos del ucf de la FPGA obtenemos la visualización de nuestros datos..

sábado, 5 de marzo de 2016

Laboratorio No 2

En la aplicación Boole se desarrolla el diseño para un decodificador alfanumérico para luego visualizar en un display de 16 segmentos. Se inicia con el diseño de las letras y números, siguiente con la combinación de entradas y salidas de acuerdo al diseño, para el caso serán 6 entradas y 16 salidas, con la aplicación Boole se genera el código en VHDL

para luego exportar el archivo generado por la aplicación al programa XilinK para hacer el esquemático con los flip flops para la secuencia de conteo, el decodificador alfanumérico y el display de 16 segmentos para la visualización.

Esquema del diseño

viernes, 4 de marzo de 2016

Laboratorio 3

Descripción

de la implementación.

Circuito esquematico.

Entrega del laboratorio

Laboratorio 1

Grupo N: 8CN

María Rosa Villazon Cerquera

Jeisson David Barreto malaver

Edison Alexander Suarez Rodríguez

Se implementó un contador

hexadecimal el cual realizo conteo de 0 hasta 15. El programa se realizó con código

en VHDL teniendo en cuenta la respectiva tabla de verdad, para este caso se requirió

de cuatro entradas y siete salidas y un visualizador display de siete segmentos;

El desarrollo del código se realizó

de la siguiente manera: nuevo

proyecto en esquemático y le adicionamos como Source que se ha elaborado en

Boole, luego de esto le colocamos (;) a las ecuaciones para que permita sintetizar, adicionamos

también el código .ucf que es de la FPGA, para luego activar y renombrar los puertos

que deseamos utilizar, y por ultimo le damos clic Check Syntax y después

Create Schematic Symbol para generar el esquemático, vamos a la pantalla

de esquemático y lo buscamos del archivo del nombre del proyecto, y luego lo

ponemos terminales y las renombramos según la necesidad. Sintetizamos todo,

implementamos diseño y se genera el archivo .bit, y está listo para programar la FPGA .

Suscribirse a:

Comentarios (Atom)